ELECTRONICA DIGITAL

Anuncio

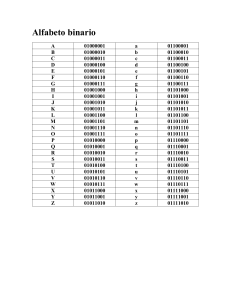

ELECTRONICA DIGITAL 1. 2. 3. 4. 5. 6. 7. 8. 9. 10. Fundamentos Funciones básicas Combinaciones entre funciones básicas Propiedades de las funciones AND y OR .Teorema de Morgan Función exclusive OR, XOR Representación de puertas lógicas según distintas normativas Simplificación de funciones lógicas Implementación de circuitos con puertas NAND y NOR. Circuitos combinacionales. Circuitos secuenciales 1. FUNDAMENTOS a)Tipos de señales Una señal es la variación de una magnitud que permite transmitir información. Las señales pueden ser de dos tipos: a.1)Señales analógicas Pueden adquirir infinitos valores entre dos extremos cualesquiera. La variación de la señal forma una gráfica continua. Señal Max Min t a.2)Señales digitales Pueden adquirir únicamente valores concretos, es decir, no varían a lo largo de un continuo. Por ejemplo , el estado de una bombilla sólo puede tener dos valores (0 apagada, 1 encendida). A cada valor de una señal digital se le llama bit y es la unidad mínima de información. Señal 1 0 b)Representación de las señales digitales Las señales digitales pueden representarse de dos maneras distintas: b.1. Cronogramas Son diagramas señal-tiempo. Vamos a explicarlo con dos ejemplos Ejemplo 1: Circuito con pulsador y bombilla P Ejemplo 2: Circuito con pulsador y dos bombillas B P B1 -Psin pulsar=0 -Ppulsado=1 B2 -Bombilla OFF=0 -Bombilla ON=1 P -Psin pulsar=0 -Bombilla1 OFF=0 -Bombilla2 OFF=0 -Ppulsado=1 -Bombilla1 ON=1 -Bombilla2 ON=1 1 0 t B P 1 1 0 t 0 t B1 1 0 t B2 1 0 t b.2) Tabla de verdad En este tipo de representación no se utiliza el tiempo. Es una tabla en la que se presentan las señales de entrada sí como las señales de salida que corresponden a cada estado. También en este caso lo mostraremos con ejemplos: Ejemplo 1: Circuito con pulsador y bombilla P B -Psin pulsar=0 -Ppulsado=1 P 0 1 -Bombilla OFF=0 -Bombilla ON=1 B 0 1 Ejemplo 2: Circuito con pulsador y dos bombillas P B1 B2 P 0 1 B1 1 1 B2 1 0 P1 0 0 0 0 1 1 1 1 P2 0 0 1 1 0 0 1 1 P3 0 1 0 1 0 1 0 1 Ejemplo 3: Circuito con tres pulsadores y una bombilla P1 B P2 P3 B 0 1 1 1 1 1 1 1 c)Sistema binario Los ordenadores y en general todos los sistemas que utilizan electrónica digital utilizan el sistema binario. En la electrónica digital sólo existen dos estados posibles (1 o 0) por lo que interesa utilizar un sistema de numeración en base 2, el sistema binario. El sistema decimal utiliza las cifras 0, 1, 2, 3, 4, 5, 6, 7, 8, 9. Veremos ahora la conversión de un sistema a otro. c.1) Transformación de decimal a binario NUMEROS ENTEROS: Se divide el número en decimal por dos hasta que el último cociente sea inferior a 2 Ejemplo 1: Paso de 18 en decimal a binario Ejemplo 2: Paso de 27 en decimal a binario 18 | 2 0 9|2 1 4 |2 0 2|2 0 1 27 | 2 1 13 | 2 1 6|2 0 3|2 1 1 18 => 10010 27 => 11011 NUMEROS FRACCIONARIOS: Si el número decimal no es entero sino que es una fracción menor que uno se multiplica la parte fraccionaria por dos, todas las veces necesarias hasta que se no se obtenga fracción o se obtenga la precisión deseada. Ejemplo 1: Paso de 0,36 de decimal a binario con seis dígitos de precisión Ejemplo2: Paso de 18,36 de decimal a binario con seis dígitos de precisión en la parte fraccionaria. 0,36.2 = 0,72 Primer dígito: 0 0,72.2 = 1,44 Segundo dígito:1 0,44.2 = 0,88 Tercer dígito: 0 0,88.2 = 1,76 Cuarto dígito: 1 0,76.2 = 1,52 Quinto dígito: 1 0,52.2 = 1,04 Sexto dígito: 1 Realizaremos la parte entera y la fraccionaria por separado: 18 => 10010 0,36=>0,010111 El resultado será: 0,36=>0,010111 18,36=>10010,010111 c.2) Transformación de binario a decimal Se multiplica cada una de las cifras del número en binario en potencias sucesivas de 2. Ejemplo 1: Paso de 10010 a decimal 10010 1.2 4 0.2 3 0.2 2 1.21 0.2 0 1.16 0.8 0.4 1.2 0.1 18 Ejemplo 2: Paso de 10011010,101 a decimal 10011010 ,101 1.27 0.26 0.25 1.24 1.23 0.22 1.21 0.20 1.2 1 0.2 2 1.2 3 128 16 8 2 0.5 0.125 154,625 d)Codigos binarios El sistema de numeración más adecuado para los circuitos digitales es el sistema binario. Se pueden establecer distintas correspondencias biunívocas entre los números en sistema decimal y en sistema binario. d.1) Código binario natural Consiste en la representación directa del número decimal a binario. Es decir, cada número se corresponde con su equivalente en binario. Ejemplo: 25=>11001 d.2) Códigos BCD (decimal codificado en binario) Representan el número transformando a binario cada una de las cifras decimales que lo componen por separado. Es decir para representar el número 25 se representa por un lado la cifra 2 y por otra la cifra 5. d.2.1) Código BCD natural(8421). Es un código ponderado, es decir, el número decimal equivalente se obtiene mediante la suma ponderada de los dígitos binarios que forman el código. Los pesos son 8(23), 4(22), 2(21) y1(20) , de ahí su nombre. Simplemente se transcriben las cifras decimales por separado a binario y viceversa Ejemplo: 25=> 2(0010) 5(0101) 2=0.8+0.4+1.2+0.1 5=0.8+1.4+0.2+1.1 d.2.2)Codigo Aiken(2421). Es también un código ponderado, pero ahora los pesos son 2,4,2 y 1. Siempre se empieza a sumar por la derecha Ejemplo 25=> 2 (0010) 5(1011) 2=0.2+0.4+1.2+0.1 5=2.1+0.4+1.2+1.1 d.2.3)Código exceso tres: Es no ponderado. Se suma a cada dígito 3 y luego se pasa a binario cada cifra. Ejemplo 25=> 2 (0101) 5(1000) 2=>2+3=>5=>0101 5=>5+3=>8=>1000 Correspondencia entre el código decimal y los BCD ponderados y no ponderados Decimal 0 1 2 3 4 5 6 7 8 9 8 0 0 0 0 0 0 0 0 1 1 BCD natural 4 2 0 0 0 0 0 1 0 1 1 0 1 0 1 1 1 1 0 0 0 0 1 0 1 0 1 0 1 0 1 0 1 2 0 0 0 0 0 1 1 1 1 1 BCD Aiken 4 2 0 0 0 0 0 1 0 1 1 0 0 1 1 0 1 0 1 1 1 1 BCD Exceso tres 1 0 1 0 1 0 1 0 1 0 1 0 0 0 0 0 1 1 1 1 1 0 1 1 1 1 0 0 0 0 1 1 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 0 1 0 2.FUNCIONES BÁSICAS a) Función igualdad Dos variables son iguales cuando hay una correspondencia biunívoca entre ellas. Cuando una es cierta la otra lo es también y viceversa. REPRESENTACIÓN a=b TABLA DE VERDAD a b 0 0 1 1 ANALOGÍA ELÉCTRICA a b a b PROPIEDADES 1.Reciprocidad: Si a=b => b=a b) Función complemento o negación Es aquella función en la que el valor de una variable es el contrario del de la otra REPRESENTACIÓN ab ANALOGÍA ELÉCTRICA b a a b TABLA DE VERDAD a B 0 1 1 0 c) Función suma OR Es aquella función que es cierta (1) si una o las dos entradas son ciertas (1) REPRESENTACIÓN PROPIEDADES 1.Reciprocidad: a bba 2. Doble negación: aa ANALOGÍA ELÉCTRICA a S b a+b=S a S b TABLA DE VERDAD a b S 0 0 0 0 1 1 1 0 1 1 1 1 PROPIEDADES 1.Elemento neutro: a+0=a 2. Suma con 1: a+1=1 3.Suma consigo mismo: a+a=a __ 4.Suma con complemento: a+a=1 5.Conmutativa: a+b=b+a 6. Asociativa: a+(b+c)=(a+b)+c d) Función producto AND Es aquella función que es cierta (1) cuanto todas y cada una de las variables de entrada son ciertas (1). REPRESENTACIÓN ANALOGÍA ELÉCTRICA a b S a . b=S a S PROPIEDADES b TABLA DE VERDAD a b S 0 0 0 0 1 0 1 0 0 1 1 1 1.Elemento neutro: a.1=a 2. Producto por 0: a.0=0 3.Producto consigo mismo: a.a=a __ 4.Producto con complemento: a . a=0 5.Conmutativa: a.b=b.a 6. Asociativa: a.(b.c)=(a.b).c 3.COMBINACIONES ENTRE FUNCIONES BÁSICAS a) Función suma NOR REPRESENTACIÓN (a+b)=S a S b TABLA DE VERDAD a b S 0 0 1 0 1 0 1 0 0 1 1 0 ANALOGÍA ELÉCTRICA S a b b) Función NAND REPRESENTACIÓN ______ (a . b)=S a S b TABLA DE VERDAD a b S 0 0 1 0 1 1 1 0 1 1 1 0 ANALOGÍA ELÉCTRICA S a b 4.PROPIEDADES DE LAS FUNCIONES AND Y OR. TEOREMA DE MORGAN a)Propiedades de las funciones AND y OR 1Distributiva: (a+b).c=a.c+b.c (a.b)+c=(a+c).(b+c) __ 2.Expansión: (a+b).(a+b)=a __ (a.b)+(a.b)=a 3.Absorción: a.(a+b)=a a+(a.b)=a b)Teorema de Morgan Siempre se verifican las siguientes igualdades ______ __ __ (a+b)=a . b _____ __ __ (a.b)=a + b Extendiendolo a n variables _____________ __ __ __ __ (a+b+......n)=a . b .c ....n _____________ __ __ __ __ (a.b…….n)=a+ b+ c…n 5.FUNCIÓN EXCLUSIVE OR, XOR Es aquella función en la que si las dos entradas son iguales la salida vale 0 y si son distintas vale 1 REPRESENTACIÓN a + b=S a S b TABLA DE VERDAD A b S 0 0 0 0 1 1 1 0 1 1 1 0 EXPRESION MEDIANTE SUMAS Y PRODUCTOS __ __ __ __ a + b=a . b + a . b=(a + b).(a + b) PROPIEDADES __ __ a + b=a.b+a.b __ __ a + b =(a + b).(a + b) __ a + b=a + b __ a + b=a + b __ __ a + b =a + b 6. REPRESENTACIÓN DE PUERTAS LÓGICAS SEGÚN DISTINTAS NORMATIVAS 7. SIMPLIFICACIÓN DE FUNCIONES LÓGICAS Existen varios métodos de simplificar funciones lógicas, este curso sólo veremos las siguientes: a)Por manipulación algebraica Se simplifica sustituyendo las operaciones usando todas las propiedades anteriormente descritas en cada uno de las operaciones lógicas, las leyes de Morgan, etc De las diversas representaciones que puede tomar una función, hay dos especialmente importantes llamadas formas canónicas. 1. Primera forma canónica de una función lógica es la suma de productos lógicos en los que interviene todas las variables de la función ya sea de forma directa o negada. Cada término o producto canónico se representa por mi donde i representa el valor decimal de la combinación binaria que se obtiene al sustituir por 1 las variables que aparecen en forma directa en el producto, y por 0 las que lo hacen de forma negada. Así en una función de cuatro variables A, B, C, D, m5 representa el producto A . B .C . D, ya que sustituyendo cada variable negada por cero y cada variable directa por 1 se obtiene 0101 que es la representación binaria del número 5. Se obtiene directamente a partir de la tabla de verdad figurando los términos de la salida que corresponden a 1, y no figurando los que corresponden a un 0. Las entradas con 0 se consideran negadas y las con 1 no negadas 2. Segunda forma canónica de una función lógica es un producto de sumas lógicas en las que interviene todas las variables de la función ya sea de forma directa o de forma negada. Cada término o producto canónico se representa por Mi donde i tiene el mismo significado que en la primera forma canónica. Así que en una función de cuatro variablas A, B, C, D, M5 representa la suma A + B + C + D =>0101 que es la representación binaria del número 5. Se obtiene a partir de la tabla de verdad figurando aquellos términos cuya salida es 0 y no apareciendo aquellos cuya salida es 1. Las entradas con 1 se consideran negadas y las entradas con 0 no negadas Ejemplo: A partir de la siguiente tabla de verdad halla las formas canónicas A B C S 0 0 0 0 0 0 1 0 0 1 0 1 0 1 1 1 1 0 0 1 1 0 1 1 1 1 0 1 1 1 1 0 Primera forma canónica S m2 m3 m4 m5 m6 A.B.C A.B.C A.B.C A.B.C A.B.C Segunda forma canónica S M 0.M 6.M 7 ( A B C).(A B C).(A B C) b) Tablas de Karnaugh Es un sistema para simplificar funciones lógicas complejas. Como bases fundamentales se deben establecer - Se puede simplificar únicamente en potencias de 2, es decir 1 (2 0), 2(21), 4(22), 8(23), 16(24), 32(25), etc - En cada celda solo puede cambiar un bit (dato) respecto de la anterior - Los agrupamientos se pueden hacer de múltiples modos 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 Ejemplo: Supongamos que al plantear el problema obtenemos la siguiente tabla de verdad a 0 0 0 0 1 1 1 1 b 0 0 1 1 0 0 1 1 c 0 1 0 1 0 1 0 1 S 1 0 1 1 1 0 0 0 1. Lo siguiente que hacemos es plantear la tabla de Karnaugh, trasladando las combinaciones de la tabla de verdad a esta nueva tabla.Obsevese como de una columna a otra sólo cambia un bit. AB C 0 0 1 0 0 1 1 1 1 0 1 1 0 1 0 1 0 0 2. A continuación nos fijamos en que tiene en comun cada agrupación y obtenemos la función lógica ___ ___ ___ ___ ___ S= C . B + C . A + A . B 3. Por último planteamos el esquema o circuito lógico A B S C 8. IMPLEMENTACIÓN DE CIRCUITOS CON PUERTAS NAND Y NOR Los fabricantes suelen fabricar los circuitos lógicos con puertas NAND o NOR debido a su bajo precio. Para convertir un circuito a puertas NAND o NOR hay que usar los teoremas de Morgan tantas veces como sea necesario hasta que toda la función se exprese con circuitos negados. Ejemplo: Implementar con puertas NAND la función : S a.b.c a.b.c a.b.c Aplicamos la doble negación a la suma S (a.b.c a.b.c a.b.c) (a.b.c).(a.b.c).(a.b.c) Ejemplo: Implementar con puertas NOR la función : S a.b.c a.b.c a.b.c Aplicamos la doble negación S (a.b.c a.b.c a.b.c) Aplicamos una doble negación a cada término S (a.b.c) (a.b.c) (a.b.c) (a b c) (a b c) (a b c) 9. CIRCUITOS COMBINACIONALES Son aquellos circuitos que se construyen con las puertas lógicas descritas anteriormente. Se les llama combinacionales puesto que la salida depende únicamente de las distintas combinaciones entre las entradas y no de estados anteriores ni del tiempo. a) Codificadores Son circuitos que poseen n salidas y 2n entradas, de tal forma que al activarse las entradas en la salida aparece la combinación binaria correspondiente al número decimal asignado a dicha entrada. El valor binario de las salidas puede ser cualquier el de cualquiera de los códigos descritos en apartados anteriores (binario natural. BCD natural, BCD Aiken, etc) Los codificadores pueden ser con o sin prioridad. Codificador sin prioridad: No puede activarse más de una entrada al mismo tiempo. No se suelen usar. Codificador con prioridad:En caso de producirse acciones simultaneas de varias de sus entradas, en la salida se presentará el código de aquella entrada tenga asignada un mayor peso, normalmente la de mayor valor decimal. Ejemplo: Diseñar un codificador de 4 a 2 lineas, con prioridad en la entrada de mayor peso. A3 A2 A1 A0 S1 S0 0 0 0 1 0 0 0 0 1 X 0 1 0 1 X X 1 0 1 X X X 1 1 Posteriormente obtendríamos las expresiones algebraicas de las salidas S0 y S1 y dibujaríamos el circuito lógico b) Decodificadores Son circuitos que poseen n entradas y un número de salidas menor o igual a 2 n, y basicamente convierten la información codificada en información sin codificar. Hay dos tipos fundamentales: b.1) Uno de N: Para cada combinación de entradas sólo se activa una de las salidas. El más típico es el decodificador BCD-Decimal, en el que se activa la salida cuyo número coincide con el número en binario expresado por las entradas. Ejemplo: Diseñar un decodificador BCD-Decimal de 2 a 4 lineas. A1 A0 S3 S2 S1 S0 0 0 0 0 0 1 0 1 0 0 1 0 1 0 0 1 0 0 1 1 1 0 0 0 Posteriormente obtendríamos las expresiones algebraicas de las salidas S0, S1, S2 y S3 y dibujaríamos el circuito lógico b.2)Decodificadores con activación simultanea de varias salidas: Permiten activar varias salidas a la vez según la combinación deseada. El más típico es el decodificador BCD-7 segmentos usadoi en los displays de calculadoras, relojes, etc. Las salidas se notan como a,b,c,d,e,f y g c) Convertidores de código Sirven para cambiar de código (de BCD natural a Aiken, de binario natural a Aiken, de BCD natural a binario natural, etc). Ejemplo: Diseñar un convertidor de tres bits de BCD natural a Aiken BCD Aiken Nº a b c d A B C D 0 0 0 0 0 0 0 0 0 1 0 0 0 1 0 0 0 1 2 0 0 1 0 0 0 1 0 3 0 0 1 1 0 0 1 1 4 0 1 0 0 0 1 0 0 5 0 1 0 1 1 0 1 1 6 0 1 1 0 1 1 0 0 7 0 1 1 1 1 1 0 1 8 1 0 0 0 1 1 1 0 9 1 0 0 1 1 1 1 1 d))Multiplexores o multiplexadores Canalizan varias fuentes de información binaria hacia una linea común de salida. Según lo que indiquen las entradas de selección tendremos como salida una u otra de las entradas de información. Se realiza uniendo las entradas con AND y el conjunto con OR. Suelen poseer 2n entradas de información, n entradas de selección y una sola salida W. Ejemplo: Diseñar un multiplexor de cuatro entradas y dos entradas de selección. S0 S1 W 0 0 I0 I0 0 1 I1 1 0 I2 1 1 I3 I1 I 0 S 0 .S 1 I 1 S 0 .S 1 I 2 S 0 .S 1 I 3 S 0 .S 1 I2 W I3 S0 S1 e) Demultiplexores o demultiplexadores Realizan una función contraria a los anteriores dirigiendo la información a la salida seleccionada mediante las entradas de control. f) Comparadores Son circuitos que detectan las relaciones mayor (M >), menor (m <) e igual (I =). Presentan dos grupos de n lineas de entrada (A y B) que son la expresión en binario de los números que queremos comparar y tres lineas de salida (M, I , m). g) Operaciones en sistema binario g.1.SUMA: Se realiza de manera análoga a la decimal. Se comienza sumando individualmente los dígitos binarios que corresponden al bit manos significativo (el de la derecha) y que ocupan la misma posición, teniendo en cuenta el acarreo (lo que nos llevamos) resultante de la suma correspondiente a la posición anterior. Ejemplo: Sumar 543 y 226 en binario Primero pasamos ambos números a binario: -543=1000011111 -226=11100010 Procedemos a efectuar la suma: Sistema decimal Sistema binario 543 + 226 769 1111111 . 1000011111 + 11100010 1100000001 Acarreo Sumando1 Sumando2 Suma En la tabla siguiente se describen todas las posibles combinaciones de sumas y los acarreos correspondientes. a 0 0 0 0 1 1 1 1 b 0 0 1 1 0 0 1 1 Cn 0 1 0 1 0 1 0 1 S 0 1 1 0 1 0 0 1 Cn+1 0 0 0 1 0 1 1 1 Donde Cn es el acarreo de la suma anterior (de bits sumados antes de esta operación), S es la suma y Cn+1 es el acarreo de la suma actual. Obtenemos que: S a.b.Cn a.b.Cn a.b.Cn a.b.Cn S Cn (a b) Cn 1 a.b.Cn a.b.Cn a.b.Cn a.b.Cn Cn 1 (b.Cn ).( a.Cn ).( a.b) Estas serían las funciones para la suma de las parejas de bits Un sumador completo de números de varios bits tendría que incluir tantos módulos como bits tienen los módulos a sumar. A continuación se describe el esquema de un sumador de números de 4 bits, donde cada Cn+1 se convierte en la en la entrada Cn del siguiente módulo g.2 DIFERENCIA: Se realizaría de manera similar, utilizando acarreos: Ejemplo: Restar 543 y 226 en binario Primero pasamos ambos números a binario: -543=1000011111 -226=11100010 Procedemos a efectuar la resta: Sistema decimal Sistema binario 1111 . Acarreo 543 1000011111 Minuendo - 226 - 11100010 Sustraendo 317 100111101 Resta En circuitería electrónica la diferencia se hace con los complementos que permiten realizar la resta con un circuito sumador, para integrar en el hardware unicamente la suma y no la suma y la resta lo que complicaría el circuito. Para ello se utilizan dos métodos, el método del complemento a uno y el de complemento a dos. Método del complemento a dos: -El complemento a dos de un número binario se obtiene cambiando los 1 por los 0 y los 0 por los 1, sumándolo al resultado el valor 1. Si uno de los números tiene menos bits que el otro previamente se le añaden ceros delante -Además se debe añadir delante el bit de signo. Si el número es positivo se pone un 0 delante, si es negativo el 1, es decir, pondremos delante 1 en el minuendo si es negativo y pondremos delante 1 en el sustraendo si es positivo (porque lo estamos restando). -Si el resultado de la operación es positivo, éste aparecerá en binario normal, si el resultado es negativo aparecerá en complemento de a dos. -Si lo que se hace es la resta del tipo –a-b, a y b deben ambos complementarse y ambos deberán llevar un 1 como bit de signo Ejemplo 1. Restar 26-13 26=>11010 13=>1101; le añado 0 para que tenga los mismos bits que 26 13=>01101; complemento cambiando 1 por 0 y 0 por 1 y le añado 1; 13c=>10010+1=>13c=>10011 +26 -13 13 Bit de signo 0 11010 1 10011 1 0 01101 se desprecia Como me ha dado 0 en BS el resultado se lee directamente y es positivo 01101=>13 2. Restar 13-26 13=>1101 ; le añado 0 para que tenga los mismos bits que 26; 13=> 01101 26=>11010 ; complemento cambiando 1 por 0 y 0 por 1 y le añado 1; 26c=>00101+1=>26c=>00110 +13 -26 -13 Bit de signo 0 01101 1 00110 1 10011 Como me ha dado 1 en BS el resultado no se lee directamente, sino que está en complemento de a dos, y además se que es negativo Para deshacer el complemento primero resto 1: 10011-1=10010 A continuación cambio los 1 por 0 y viceversa obteniendo el resultado -01101=>-13 Método del complemento a uno: -El complemento a uno de un número binario se obtiene cambiando los 1 por los 0 y los 0 por los 1. Si uno de los números tiene menos bits que el otro previamente se le añaden ceros delante -Además se debe añadir delante el bit de signo. Si el número es positivo se pone un 0 delante, si es negativo el 1, es decir, pondremos delante 1 en el minuendo si es negativo y pondremos delante 1 en el sustraendo si es positivo (porque lo estamos restando). -Si el resultado de la operación es positivo, éste aparecerá en binario normal, si el resultado es negativo aparecerá en complemento de a uno. -Si hay un acarreo del bit de signo este se suma al resultado total. -Si lo que se hace es la resta del tipo –a-b, a y b deben ambos complementarse y ambos deberán llevar un 1 como bit de signo Ejemplo 1. Restar 26-13 26=>11010 13=>1101; le añado 0 para que tenga los mismos bits que 26 13=>01101; complemento cambiando 1 por 0 y 0 por 1; 13c=>10010 +26 -13 13 Bit de signo 0 1 1 0 0 0 11010 10010 01100 +1 01101 Como me ha dado 0 en BS el resultado se lee directamente y es positivo 01101=>13 2. Restar 13-26 13=>1101 ; le añado 0 para que tenga los mismos bits que 26; 13=> 01101 26=>11010 ; complemento cambiando 1 por 0 y 0 por 1; 26c=>00101 +13 -26 -13 Bit de signo 0 01101 1 00101 1 10010 Como me ha dado 1 en BS el resultado no se lee directamente, sino que está en complemento de a uno, y además se que es negativo Para deshacer el complemento cambio los 1 por 0 y viceversa obteniendo el resultado -01101=>-13 10.CIRCUITOS SECUENCIALES Son aquellos cuya salida en cualquier momento no depende sólo de la entrada al circuito sino tambien de la secuencia de entradas a las que estuvo sometido anteriormente. Pueden clasificarse en dos grandes grupos: 1. Asíncronos: Los cambios de estado se producen cuando están presentes las entradas adecuadas con los retrasos inherentes a las velocidades finitas de conmutación de los dispositivos físicos utilizados. 2. Síncronos: Los cambios de estado se producen cuando además de estar presentes las entradas adecuadas se produce la transición de una señal compartida por los elementos del sistema y que sincroniza su funcionamiento. A esta señal se le llama señal de reloj o de clock a). Biestables o flip-flops Son los elementos básicos para construir los circuitos secuenciales. Se caracterizan por poseer memoria, es decir, tienen en cuenta las entradas anteriores que ha tenido el circuito. Pueden construirse a partir de puertas lógicas o comprarse en forma de circuitos integrados. b). Biestables asíncronos Son fundamentalmente los biestables R-S (Set-Reset) y aunque los demás que veremos a continuación pueden considerarse asíncronos (si se elimina la entrada de reloj), en general no lo son, así que consideraremos como asíncrono sólo el R-S. b.1 Biestable R-S Es un circuito marcha-paro. Posee dos entradas llamadas Set y Reset y dos salidas Q y Q. Un 1 en S pone Q en 1 y Q en 0; un 1 en R pone Q en 0 y Q en 1 . S Q . R Q . R S Q Q 0 0 Qn Qn 0 1 1 0 1 0 0 1 1 1 ? ? Los biestables R-S se pueden construir con puertas NAND y con puertas NOR Q Q S S R R c) Biestables síncronos Se encuentran regulados por la entrada del reloj (clock). El gobierno que ejerce el clock se puede realizar de distintas maneras: 1. Sensible al nivel El FF se activa cuando el nivel del clock es 1 2. Sensible al flanco (edge triggered) El FF se activo con los flancos o de subida o de bajada de la señal del clock 3. Maestro-esclavo (master-slave) Se basa esencialmente en dos FF seguidos. El primero es gobernado a flanco de subida (maestro) y el segundo por el de bajada (esclavo). Se recogen los datos durante el flanco de subida y se proporcionan las salidas durante el flanco de bajada, así se consigue separar los periodos de entrada de datos con los de salida de datos. Los biestables síncronos más típicos son los siguientes: c.1) FF tipo D D D Q Q Clock C Q Q D Qn+1 0 0 1 1 T Qn+1 0 Qn 1 Qn J K Qn+1 0 0 Qn 0 1 0 1 0 1 c.2) FF tipo T T T Q Q Clock C Q Q c.3) FF tipo JK J K Clock J K Q Q C Q Q 1 1 Qn Se puede observar que si J y K son iguales actúa como un T y que si J y K son distintos actúa como un D. c.4 Equivalencias entre FF JK=>T J K Clock J K Q Q C Q Q JK=>D J K Clock J K Q Q C Q Q d) Diseño de contadores síncronos Se diseñan usando FF que reciben el golpe de reloj al mismo tiempo a) Tablas de excitación Son tablas que reflejan las entradas y las salidas para obtener un cambio en la salida D Qn+1 D Qn Qn+1 0 0 0 0 0 1 1 1 0 1 0 1 0 1 1 1 T Qn+1 T Qn Qn+1 0 Qn 0 0 0 1 Qn 1 0 1 1 1 0 0 1 1 J K Qn+1 J K Qn Qn+1 0 0 Qn 0 X 0 0 0 1 0 1 X 0 1 1 0 1 X 1 1 0 1 1 Qn X 0 1 1 b) Método genérico de construcción Ejemplo: Se desea construir un contador de subida de 0 a 4 usando FF tipo JK 1.- Se pone el mayor número de la secuencia en binario 4=> 1 0 0 3erFF 2ºFF 1erFF Q3 Q2 Q1 2.-Se construye la siguiente tabla Q3 Q2 Q1 0 1 2 6 4 0 0 0 0 0 1 0 0 0 1 1 0 0 0 1 0 1 0 0 3erFF J3 K3 2ºFF J2 K2 1erFF J1 K1 0=>0 0=>0 0=>0 0=>1 1=>0 0 X 0 X 0 X 1 X X 1 0=>0 0=>1 1=>1 1=>0 0=>0 0 X 1 X X 0 X 1 0 X 0=>1 1=>0 0=>1 1=>0 0=>0 1 X X 1 1 X X 1 0 X 3.-Se construyen tablas de Karnaugh para cada FF 3erFF Q3Q2 00 01 11 10 Q1 Q3Q2 01 11 10 0 0 0 1 X X X X Q1 0 1 0X 0X XX X1 0X 1X XX XX Q3Q2 00 01 11 10 Q3Q2 01 11 10 0 1 X X X X 0 X Q1 0X X0 XX 0X 1X X1 XX XX Q3Q2 00 01 X X Q3Q2 11 10 X X 1 X Q1 0 1 0 1 X X Q3Q2 0 1 X X X X K2=Q1 00 01 11 10 1 X 1 X X X 0 X Q1 1X 1X XX 0X X1 X1 XX XX X X 00 01 11 10 J2=Q1 Q1 0 1 0 1 K3=1 00 J2K2 1erFF 00 01 11 10 J3=Q2.Q1 Q1 0 1 Q3Q2 Q1 0 1 J3K3 2ºFF 00 Q3Q2 00 01 11 10 Q1 0 1 J1K1 0 1 X 1 J1=Q3 X 1 X X X X K1=1 4.-Representamos el circuito lógico anterior 1 J1 K1 C Q1 J2 1 K2 Q1 C Q1 Q2 J3 2 K3 Q2 C Q2 Q3 3 Q3 Q1 e) Otros circuitos síncronos Contador de anillo 1 0 0 1 0 0 0 1 1 0 0 0 1 0 0 Contador Jhonson 0 0 1 0 1 1 1 1 0 1 0 0 0 0 0 1 1 1 1. Transforma los siguientes cronogramas en tablas de verdad. NOTA : E=Entrada S=Salida a) b) E1 E1 E2 E2 S S E3 E3 S S 2. Realiza las tablas de verdad de los siguientes circuitos eléctricos: a) b) 3. Transforma los siguientes números al sistema binario (los decimales con 6 dígitos de precisión): a) 125,123 b)240,67 4. Transforma los siguientes números binarios a decimales : a)11010011,11001 b) 111111,11010 5 Expresa en código binario natural, BCDnatural, Aiken y exceso tres los siguientes números a)213 b)145 6 Los siguientes número están expresado en código Aiken. Conviertelos al resto de los códigos a) 00101011 b)111111 c)10101 7. Halla la tabla de verdad de los siguientes circuitos: a) A B C S A B C e) A B C A B C b) S f) S S 7.Para el aprovisionamiento de un pueblo, se dispone de un depósito que se llena con el agua que se bombea desde una presa. La bomba es accionada cuando se cumplen las dos condiciones siguientes : Cuando el nivel del depósito ha descendido hasta un nivel mínimo por lo que es necesario suministrarle agua. El nivel de la presa es superior a un nivel máximo predeterminado. Escribe la tabla de verdad para el sistema de control de la bomba , halla las formas canónicas y diseña el circuito lógico de control a partir de la simplificación por Karnaugh. Nivel máximo de la presa Bomba Nivel mínimo del depósito 8. Diseñar un sistema en el que dado en binario un número del 0 al 7, nos indique si dicho número se encuentra entre el 0 y el 5, ambos incluidos (salida X1) ; y si dicho número está entre el 3 y el 7 ambos incluidos (salida X2). Escribe la tabla de verdad para el sistema, halla las formas canónicas y diseña el circuito lógico de control a partir de la simplificación por Karnaugh. 9. En una fabrica de conservas se desea que se puedan enlatar las siguientes combinaciones: -Judias viudas -Judias con Chorizo -Judias con Chorizo y Morcilla -Lentejas viudas -Lentejas con Morcilla -Lentejas con Judias con Chorizo y con Morcilla. Escribe la tabla de verdad para el sistema, halla las formas canónicas y diseña el circuito lógico de control a partir de la simplificación por Karnaugh. 10. Se desea construir un ascensor en un edificio que consta de 10 plantas mas planta baja. Como hay plantas que no deben tener servicio para el público porque pertenecen a una zona restringida, el ascensor sólo debe poder parar en las plantas 0, 1, 2, 6, 9, 10. Escribe la tabla de verdad para el sistema, halla las formas canónicas y diseña el circuito lógico de control a partir de la simplificación por Karnaugh. 11. Transforma a puertas NAND y NOR las siguientes funciones. Dibuja tambien los circuitos de control. a ) S a.b.c a.b.c a.b.c a.b.c a.b b) S a.b.c.d a.b.c b.c b 12. Diseña un codificador con prioridad de 8 a 3 lineas. Escribe la tabla de verdad para el sistema, halla las formas canónicas y diseña el circuito lógico de control a partir de la simplificación por Karnaugh. 13. Halla la tabla de verdad de un decodificador BCD-7segmentos. A F B G E C D 14. Halla la tabla de verdad de un decodificador Uno de N de 3 a 8 líneas.. 15. Halla la tabla de verdad de un convertidor de tres bits de Aiken a exceso 3. 16. Diseña un multiplexor de 8 entradas y tres entradas de selección. Diseña el circuito lógico. 17. Diseña un comparador de números de dos bits. Escribe la tabla de verdad para el sistema, halla las formas canónicas y diseña el circuito lógico de control a partir de la simplificación por Karnaugh. 18 Suma en binario los siguientes números: a) 25+15 b)30+48 c) 11+21 19. Resta por los métodos de complemento de a dos y de complemento de a uno los números siguientes: a) 41-21 b)23-14 c)8-19 d) 121-143 20.Dibuja los cronogramas de salida de los siguientes flip-flops: D (entrada) C (clock) Q(flanco subida) Q(flanco bajada) Q( master-slave) T (entrada) C (clock) Q(flanco subida) Q(flanco bajada) Q( master-slave) D (entrada) C (clock) Q(flanco subida) Q(flanco bajada) Q( master-slave) T (entrada) C (clock) Q(flanco subida) Q(flanco bajada) Q( master-slave) D (entrada) C (clock) Q(flanco subida) Q(flanco bajada) Q( master-slave) 21. Diseñar un contador síncrono que cuente de 3 a 0 (es decir, 3-2-1-0-3) usando: a) FF tipo D b) FF tipo T c) FF tipo JK 22.Diseña una secuencia de luces como la siguiente: (0) Usa FF tipo JK (1) 21) a)Tipo D b) Tipo T c) Tipo JK 22)